July 25, 2018

एक सीधी चढ़ाया तांबे (डीपीसी) मेटालाइज्ड सब्सट्रेट तकनीक को इस आलेख में पेश किया गया है और इसकी विशेषता है। प्रस्तावित डीपीसी मेटालाइज्ड सब्सट्रेट उत्कृष्ट थर्मल प्रबंधन और उच्च आवृत्ति विशेषताओं के मुख्य फायदे प्रदान करता है, टी के कारण ...

मेटालाइज्ड सिरेमिक सब्सट्रेट पर सीधी चढ़ाया तांबा (डीपीसी) प्रक्रिया मूल रूप से प्रत्यक्ष विद्युत, थर्मल और यांत्रिक प्रदर्शन की वजह से प्रत्यक्ष बंधुआ तांबा (डीबीसी) प्रक्रिया को प्रतिस्थापित करने के लिए बनाई गई थी। 1 डीबीसी की तुलना में, डीपीसी एक पतली फिल्म बंधन परत के उपयोग के कारण, अल 2 ओ 3 / एलएन सब्सट्रेट और तांबा धातु के बीच एक बहुत मजबूत बंधन शक्ति प्रदान करता है। तांबे की परत के लिए 2 डीपीसी की मोटाई नियंत्रण में बहुत पतली से बहुत मोटी तक अच्छी क्षमता होती है। ठीक पिच डिजाइन के लिए, न्यूनतम कंडक्टर लाइन चौड़ाई / 3 मिलियन की दूरी आसानी से प्राप्त की जा सकती है, और छेद के माध्यम से तांबे से अच्छे विद्युत और थर्मल विशेषताओं के लिए भर जाते हैं। प्रस्तावित डीपीसी सब्सट्रेट का उपयोग करके, बेहतर प्रदर्शन अन्य सुविधाओं की तुलना में अन्य प्रौद्योगिकियों की तुलना में प्राप्त किया जा सकता है, जिसमें उच्च सर्किट घनत्व, उत्कृष्ट उच्च आवृत्ति विशेषताओं, उत्कृष्ट थर्मल प्रबंधन और ताप हस्तांतरण प्रदर्शन, बकाया सोल्डरता और तार शामिल हैं। असेंबली विशेषताओं को बंधन। इसलिए इन डीपीसी सबस्ट्रेट्स को उच्च आवृत्ति घटकों के लिए व्यापक रूप से उपयोग किया जा सकता है जिसके लिए उच्च शक्ति और उच्च गर्मी की आवश्यकता होती है।

इस लेख में, डीपीसी फैब्रिकेशन को इस प्रक्रिया के कई महत्वपूर्ण विशेषताओं को पेश करने के लिए संक्षेप में एक प्रक्रिया प्रवाह चार्ट के साथ वर्णित किया गया है। डीपीसी सब्सट्रेट के लिए एक साधारण विद्युत विशेषता का उपयोग उच्च आवृत्ति ढांकता हुआ निरंतर और अपव्यय कारक निकालने के लिए किया जाता है। अंत में, एक 10 गीगाहर्ट्ज, समांतर-युग्मित रेखा बैंडपास फ़िल्टर निकाले गए ढांकता हुआ पैरामीटर और डीपीसी मेटालाइज्ड सब्सट्रेट के उत्कृष्ट उच्च-आवृत्ति प्रदर्शन को सत्यापित करने के लिए डिज़ाइन किया गया है।

प्रत्यक्ष चढ़ाया कॉपर प्रक्रिया

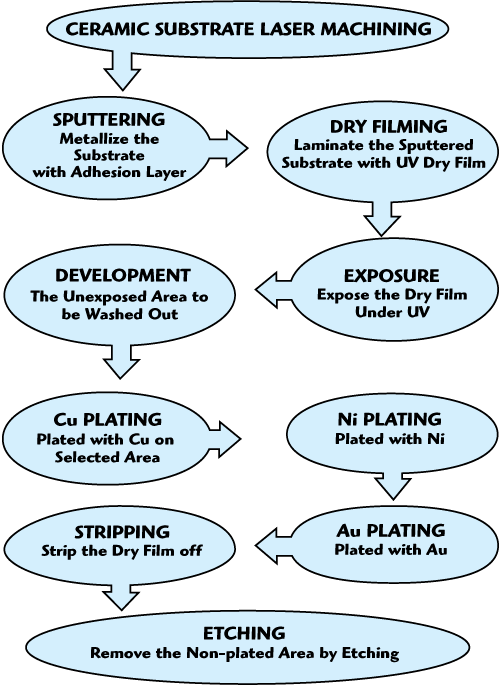

पूरी डीपीसी प्रक्रिया में मूल रूप से चित्रा 1 में प्रदर्शित चरणों को शामिल किया गया है, जिसमें सिरेमिक सब्सट्रेट में छेद परिभाषित करना, सिरेमिक सब्सट्रेट पर एक तांबा फिल्म को छिड़काव करना, तांबा फिल्म पर एक सूखी फिल्म बनाना, एक्सपोजर और विकास, चढ़ाना के साथ एक सर्किट आरेख बनाना तांबे की ओर जाता है, शुष्क फिल्म को हटाता है और बीज धातु तांबे को नक़्क़ाशी देता है। 3 विस्तृत प्रक्रियाओं का वर्णन एसपी रु, 4 और सैद्धांतिक स्पष्टीकरण और चित्रों के साथ किया गया है।

चित्रा 1 डीपीसी प्रक्रिया प्रवाह चार्ट।

प्रवाह चार्ट दिखाए जाने के साथ, लेजर के साथ नंगे सिरेमिक सब्सट्रेट पर छेद को परिभाषित करके डीपीसी प्रक्रिया शुरू की जाती है। इन छेदों को सिरेमिक सब्सट्रेट के दोनों किनारों के बीच संवाद करने के लिए छेद के माध्यम से उपयोग किया जा सकता है यदि यह कुछ विशिष्ट डिजाइन किए गए लेआउट के लिए आवश्यक है। फिर एक तांबे की फिल्म, जिसे बीज धातु परत के रूप में उपयोग किया जाता है, सिरेमिक सब्सट्रेट के विपरीत किनारों पर घिरा हुआ है ताकि यह एक तांबा परत से ढका हुआ हो। सर्किट आरेख का वर्णन करने वाली कलाकृति से, पारंपरिक फोटोमास्क प्रौद्योगिकी का उपयोग करके एक फोटोमास्क बनाया जाता है। फोटोमास्क स्पष्ट रूप से स्थित है और सिरेमिक सब्सट्रेट पर सूखी फिल्म का पालन करता है, जिसे एक खुला कक्ष में भेजा जाता है।

उजागर कक्ष में वैक्यूम बनाने के बाद, पराबैंगनी किरणें फोटोमास्क के माध्यम से सूखी फिल्म को विकिरण करती हैं, जो पराबैंगनी विकिरण द्वारा बहुलक होती है। सूखी फिल्म, जो पराबैंगनी किरणों से विकिरण नहीं होती है, प्रतिक्रिया नहीं करती है और इसकी रासायनिक संरचना को रोकती है। विकास प्रक्रिया सूखी फिल्म के बहुलक हिस्से को रासायनिक सफाई या शारीरिक सफाई से जोड़ती है। इस तरह, तांबा फिल्म के कुछ हिस्सों को सूखी फिल्म से उजागर किया जाता है; तांबा फिल्म के उन हिस्सों में सिरेमिक सब्सट्रेट पर एक सर्किट के आवश्यक तांबा क्षेत्रों का उत्पादन करने के लिए सर्किट की कलाकृति के अनुसार आवश्यक सर्किट आरेख तैयार किया जाएगा। इस प्रकार, सर्किट लेआउट सूखी फिल्म पर मुद्रित किया जा सकता है।

कॉपर सर्किट बनाने के लिए एक चढ़ाना तकनीक द्वारा उपयुक्त कंडक्टर मोटाई और चौड़ाई के साथ, सिरेमिक सब्सट्रेट पर शुष्क फिल्म के उजागर हिस्सों को भरने के लिए कॉपर जमा किया जाता है। उपर्युक्त प्रक्रियाओं के अनुसार, धातुकृत सर्किट क्षेत्र में पतला, सपाट और चिकनी विशेषताएं होती हैं, और गर्मी का अपव्यय अच्छा होता है। फिर तांबे की ऊपरी सतह पर निकल और सोना जमा किया जाता है। निकल फिल्म तांबे की परमाणुओं को सोने की फिल्म में फैलाने से रोकती है। सोना फिल्म कंडक्टर सतह के ऑक्सीकरण से बचाती है और सोने के बंधन तारों के लिए आसंजन में सुधार करती है। तांबे की ऊपरी सतह पर एक ऑप्टिकल प्रतिरोध बनता है। सिरेमिक सब्सट्रेट पर शेष सूखी फिल्म को हटा दिया जाता है। सूखी फिल्म को अलग करने के बाद, तांबा सर्किट निकल और सोने की फिल्मों द्वारा संरक्षित है। अलग तांबा फिल्म प्रक्रिया तांबा फिल्म ऑप्टिकल प्रतिरोध से संरक्षित नहीं है।

वर्णित प्रक्रियाओं और उपयोग की जाने वाली सामग्रियों के कारण, डीपीसी प्रक्रिया के कई महत्वपूर्ण विशेषताओं को संक्षेप में सारांशित किया जा सकता है:

सुपीरियर थर्मल प्रदर्शन

कम विद्युत प्रतिरोध कंडक्टर लाइनें

तापमान> 340 डिग्री सेल्सियस तक स्थिर

स्वचालित, बड़ी प्रारूप असेंबली के साथ संगत सटीक सुविधा स्थान

· ठीक लाइन रिज़ॉल्यूशन डिवाइस और सर्किट्री की उच्च घनत्व की इजाजत देता है

सिद्ध विश्वसनीयता

यांत्रिक रूप से ऊबड़ सिरेमिक निर्माण

कम लागत, उच्च प्रदर्शन सिरेमिक समाधान

डीपीसी मेटालाइज्ड सब्सट्रेट के अनुप्रयोगों को उच्च सांद्रता एलईडी (एचबीएलडीडी), सौर सांद्रता कोशिकाओं, पावर अर्धचालक पैकेजिंग और मोटर वाहन मोटर नियंत्रण के लिए सब्सट्रेट पर चुना जा सकता है। इसके अलावा, उत्कृष्ट विद्युत प्रदर्शन के साथ डीपीसी सब्सट्रेट आरएफ / माइक्रोवेव घटकों के लिए विचार किया जा सकता है, जिसके लिए बहुत कम नुकसान की आवश्यकता होती है।

विद्युत गुण निष्कर्षण

आरएफ / माइक्रोवेव अनुप्रयोगों के लिए डीपीसी सबस्ट्रेट्स का उपयोग करने के लिए, ढांकता हुआ गुण निकाला जाना चाहिए। इलेक्ट्रॉनिक पैकेजिंग डिज़ाइन के लिए डाइलेक्ट्रिक कैरेक्टरेशन एक बहुत ही महत्वपूर्ण मुद्दा है क्योंकि विद्युत व्यवहार उच्च आवृत्तियों पर ढांकता हुआ निरंतर और ढांकता हुआ नुकसान से बहुत प्रभावित होता है।

चित्रा 2 डीपीसी माइक्रोस्ट्रिप समानांतर कनेक्शन के साथ समांतर-युग्मित रेज़ोनेटर: (ए) पीसीएमआर 1 और (बी) पीसीएमआर 4।

प्रकाशित साहित्य में कई रिपोर्ट किए गए तरीके हैं। 5-8 इनमें से कई विधियों में एक या कई सीमाएं हैं, जैसे महंगा और जटिल उपकरण, कठिन-से-फैब्रिकेट फिक्स्चर, मापा गया ढांकता हुआ गुण केवल एक विशेष आवृत्ति, खराब दोहराने योग्यता, और ढांकता हुआ निरंतर और ढांकता हुआ नुकसान दोनों प्राप्त करने में असमर्थता । हालांकि, इस आलेख में, आगे सब्सट्रेट डिज़ाइन और सिमुलेशन के लिए सटीक ढांकता हुआ कारकों को प्राप्त करने के लिए एक साधारण दृष्टिकोण का उपयोग किया जाता है।

Holzman ढांकता हुआ डेटा निकालने के लिए resonator के एक कंप्यूटर मॉडल का इस्तेमाल किया। 9 एक बार सर्किट को कंप्यूटर-एडेड डिज़ाइन (सीएडी) सिम्युलेटर के साथ सटीक रूप से मॉडलिंग किया जाता है, तो सब्सट्रेट की ढांकता हुआ गुणों को सिम्युलेटर से अनुमानित विशेषताओं के साथ भविष्यवाणियों की तुलना करके निर्धारित किया जा सकता है। यह अनुभवजन्य / विश्लेषणात्मक दृष्टिकोण माइक्रोवेव क्षेत्र में कई शोधकर्ताओं द्वारा प्रदर्शित किया गया है।

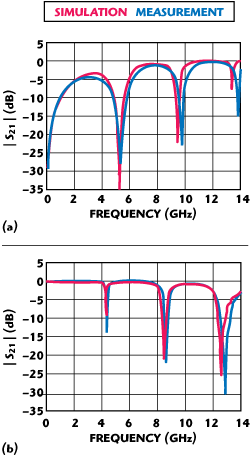

चित्रा 3 चित्रा 3 microstrip समानांतर-युग्मित resonators के लिए मापा और अनुरूपित परिणाम: (ए) पीसीएमआर 1 और (बी) पीसीएमआर 4।

इसलिए, डीपीसी सब्सट्रेट के लिए उच्च आवृत्ति ढांकता हुआ डेटा निकालने के लिए, दो संशोधित माइक्रोस्ट्रिप समांतर-युग्मित रेज़ोनेटर एक विस्तृत बैंडविड्थ पर अलग शून्य के साथ बनाये गये थे। चित्रा 2 समांतर-युग्मित माइक्रोस्ट्रिप रेज़ोनेटर (पीसीएमआर) की तस्वीरें दिखाता है। पीसीएमआर 1 दिखाया गया है कम आवृत्तियों पर अधिक गहराई के साथ संचरण शून्य को प्रभावित करता है; पीसीएमआर 4 उच्च आवृत्तियों पर गहराई से गहराई के साथ संचरण शून्य उत्पन्न करता है। दो रेज़ोनेटरों में समान युग्मित रेखा संरचना होती है जिसमें 570 मिलियन की रेखा दूरी और 12 मिलियन की दूरी होती है, लेकिन विपरीत आउटपुट कनेक्शन होते हैं। दो पीसीएमआर के माप से, ये शून्य ब्रॉडबैंड आवृत्ति प्रतिक्रिया के तहत अच्छी सटीकता के साथ सही ढांकता हुआ मानों को विभाजित करने के लिए पर्याप्त हैं। हालांकि, पीसीएमआर 1 और पीसीएमआर 4 के लिए पहला ट्रांसमिशन शून्य क्रमशः 5.2 और 4.2 गीगाहर्ट्ज पर है, और बैंड पर हर अनुनाद आवृत्ति पर लगभग दोहराया जाता है। अनुनादकों का प्रारंभिक सिमुलेशन करने के लिए, एडीएस मोमेंटम सिमुलेशन में डीपीसी सब्सट्रेट के लिए 9.5 का ढांकता हुआ निरंतर स्थिरांक और 0.004 का ढांकता हुआ नुकसान माना जाता था।

परीक्षण सेटअप में एजिलेंट ई 8364 ए नेटवर्क विश्लेषक, दो के-कनेक्टर कोएक्सियल इनपुट पोर्ट्स के साथ एक एंटित्सु यूनिवर्सल टेस्ट फ़िक्स्चर, और ग्राउंड-प्लेन समर्थित डीपीसी मेटालाइज्ड सब्सट्रेट को माइक्रोस्ट्रिप रेज़ोनेटर के साथ शामिल किया गया था। इसके अलावा, पीसीएमआर के समान संदर्भ विमान पर कैलिब्रेट करने के लिए डीपीसी निर्मित कैलिब्रेशन किट का उपयोग करके एक टीआरएल अंशांकन अपनाया जाता है। पीसीएमआर 1 और पीसीएमआर 4 के लिए अनुरूपित और मापा सम्मिलन नुकसान के बीच की तुलना चित्रा 3 में दिखायी गयी है।

चित्रा 4 microstrip समांतर-युग्मित resonator के लिए मापा और अनुरूपित परिणाम।

माप से, यह स्पष्ट है कि अनुमानित ढांकता हुआ मान त्रुटियों में हैं, त्रुटि उच्च आवृत्तियों में बढ़ रही है। सही ढांकता हुआ निरंतर और ढांकता हुआ नुकसान निकालने के लिए, इन मानों को आवृत्ति प्रतिक्रिया से मेल खाने के लिए एडीएस मोमेंटम में समायोजित किया जाता है जब तक अनुमानित शून्य मापित शून्य से मेल नहीं खाता। चित्रा 4 ढांकता हुआ पैरामीटर समायोजित करने के बाद, 14 गीगाहर्ट्ज तक दो पीसीएमआर के लिए फिट परिणाम दिखाता है। इस मामले में, डीपीसी सब्सट्रेट के इन दो मानकों में वृद्धि क्रमशः ढांकता हुआ नुकसान के लिए ढांकता हुआ निरंतर और 0.0004 से 0.002 के लिए 9.5 से 9 .75 तक है। ये मान उच्च आवृत्तियों पर अनुमानित डेटा से अधिक सटीक हैं और व्यापक रूप से सब्सट्रेट डिज़ाइन और सिमुलेशन के लिए उपयोग किए जा सकते हैं।

डीपीसी प्रौद्योगिकी का उपयोग कर 10 गीगाहर्ट्ज समांतर-युग्मित लाइन फ़िल्टर की चित्रा 5 तस्वीर।

माइक्रोवेव सर्किट डिजाइन

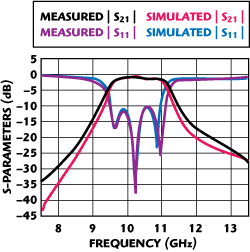

निकाले गए ढांकता हुआ डेटा की सटीकता को प्रमाणित करने के लिए, डीपीसी सब्सट्रेट पर निर्मित माइक्रोवेव फ़िल्टर का प्रदर्शन किया गया था। समानांतर युग्मित रेखा संरचना का उपयोग करते हुए यह बीपीएफ, 10 गीगाहर्ट्ज की एक केंद्र आवृत्ति है, 15 प्रतिशत की बैंडविड्थ, 0.1 डीबी बराबर-लहर प्रतिक्रिया और तीसरी क्रम टोपोलॉजी है, और चित्रा 5 में दिखाया गया है। बीपीएफ को निकाले गए ढांकता हुआ निरंतर और ढांकता हुआ नुकसान का उपयोग करके एडीएस मोमेंटम के साथ डिजाइन और अनुकूलित किया गया था। आवृत्ति रेंज को 4 से 14 गीगाहर्ट्ज तक कवर करने के लिए डीपीसी सबस्ट्रेट्स पर टीआरएल अंशांकन किट भी बनाई गई थीं।

इन परीक्षण मानकों के साथ, Anritsu परीक्षण स्थिरता के coax-to-microstrip संक्रमण और फ़िल्टर के इनपुट और आउटपुट पोर्ट तक माइक्रोस्ट्रिप लाइनों को डी-एम्बेडेड किया जा सकता है। मापा सम्मिलन हानि और वापसी का नुकसान चित्रा 6 में दिखाया गया है। इन प्रयोगात्मक परिणामों के आधार पर, फ़िल्टर प्रतिक्रिया की एक अच्छी भविष्यवाणी ईएम सिम्युलेटर में निकाले गए ढांकता हुआ मानों का उपयोग करके हासिल की जाती है। बीपीएफ का मापा सम्मिलन नुकसान 10 गीगाहर्ट्ज पर केवल 0.5 डीबी है। यह स्पष्ट रूप से प्रदर्शित करता है कि एक सिरेमिक सब्सट्रेट और तांबा कंडक्टर के साथ बनाई गई डीपीसी प्रक्रिया, उच्च आवृत्तियों पर उत्कृष्ट कम-हानि प्रदर्शन प्रदान करती है और आरएफ पैकेजिंग और माइक्रोवेव उपकरणों में उपयोग करने की उत्कृष्ट क्षमता प्रदान करती है।

चित्रा 6 10 गीगाहर्ट्ज डीपीसी समांतर-युग्मित लाइन फ़िल्टर की मापित और नकली विशेषताओं।

निष्कर्ष

यह आलेख प्रक्रिया प्रवाह, विद्युत गुण निष्कर्षण और माइक्रोवेव सर्किट डिजाइन सहित एक डीपीसी धातुकृत सब्सट्रेट प्रस्तुत करता है। सिरेमिक सब्सट्रेट और मेटालाइज्ड तांबा कंडक्टर के उपयोग के कारण, डीपीसी सब्सट्रेट अच्छी उच्च आवृत्ति विद्युत विशेषताओं को प्राप्त करता है। इस बीच, डीपीसी सब्सट्रेट के लिए ढांकता हुआ निरंतर और ढांकता हुआ नुकसान प्राप्त करने के लिए एक सरल निष्कर्षण विधि प्रस्तावित किया गया था, और 0.5 डीबी सम्मिलन हानि के साथ 10 गीगाहर्ट्ज समांतर-युग्मित रेखा बीपीएफ आगे सत्यापन के लिए बनाया गया था। यह आलेख स्पष्ट रूप से दर्शाता है कि डीपीसी मेटालाइज्ड सब्सट्रेट आरएफ और माइक्रोवेव पैकेज डिज़ाइन के लिए काफी उपयुक्त है, इसके उत्कृष्ट कम-हानि प्रदर्शन के साथ।

संदर्भ

1. एम एंटेज़िएरियन और आरएएल ड्रू, "डायपर बॉन्डिंग ऑफ कॉपर टू एल्यूमिनियम नाइट्राइड," मैटेरियल्स साइंस एंड इंजीनियरिंग , ए -212, जुलाई 1 99 6, पीपी 206-212।

2. जे। शूलज़-हार्डर, "डायरेक्ट बोडेड कॉपर सबस्ट्रेट्स के फायदे और नए विकास," माइक्रोइलेक्ट्रॉनिक्स विश्वसनीयता , वॉल्यूम। 43, संख्या 3, 2003, पीपी 35 9-365।

3. "डीपीसी-डायरेक्ट प्लेटेड कॉपर थिन फिल्म टेक्नोलॉजी," टोंग हैसिंग, www.ready-sourcing.com/sourcing-news/electronic/dpc.html ।

4. एसपी रु, "सिरेमिक सब्सट्रेट में वॉयड्स को हटाने के लिए विधि," यूएस पेटेंट, यूएस 6,800,211 बी 2, अक्टूबर 2004।

5. एमके दास, एसएम वोडा और डीएम पोजर, " माइक्रोवेव थ्योरी एंड टेक्निक्स , वॉल्यूम पर आईईईई लेनदेन ," सब्सट्रेट डाइलेक्ट्रिक कॉन्स्टेंट के मापन के लिए दो तरीके "। 35, संख्या 7, जुलाई 1 9 87, पीपी 636-642।

6. एसएच चांग, एच कुआं, एचडब्ल्यू वू, आरवाई यांग और एमएच वेंग, "माइक्रोवेव डाइलेक्ट्रिक कॉन्सटेंट का निर्धारण दो माइक्रोस्ट्रिप लाइन विधि द्वारा ईएम सिमुलेशन के साथ संयुक्त," माइक्रोवेव और ऑप्टिकल टेक्नोलॉजी लेटर्स , वॉल्यूम। 48, संख्या 11, नवंबर 2006, पीपी 21 99-2121।

7. एच। यू, केएल विरगा और जेएल प्रिंस, "एक स्ट्रिपलाइन स्थिरता का उपयोग करके डाइलेक्ट्रिक कॉन्स्टेंट और लॉस टेंगेंट मापन," घटक, पैकेजिंग और विनिर्माण प्रौद्योगिकी , भाग बी, वॉल्यूम पर आईईईई लेनदेन । 21, संख्या 4, नवंबर 1 99 8, पीपी 441-446।

8. पीए बर्नार्ड और जेएम गौत्रे, "माइक्रोसॉफ्ट रिंग रेज़ोनेटर का उपयोग करके डाइलेक्ट्रिक कॉन्सटेंट का मापन," माइक्रोवेव थ्योरी एंड टेक्निक्स , आईईईई लेनदेन पर आईईईई लेनदेन । 3 9, संख्या 3, मार्च 1 99 1, पीपी। 592-595।

9। ईएल होल्ज़मैन, "एक समानांतर युग्मित माइक्रोस्ट्रिप रेज़ोनेटर का उपयोग करके एक एफआर 4 सब्सट्रेट के डाइलेक्ट्रिक कॉन्सटेंट के वाइडबैंड मापन," माइक्रोवेव थ्योरी एंड टेक्निक्स , आईईईई लेनदेन पर आईईईई लेनदेन । 54, संख्या 7, जुलाई 2006, पीपी 3127-3130।